千兆网之SGMII解析

这一篇文章就是简单解析一下SGMII这种接口的内容。

SGMII即Serial GMII,串行GMII,收发各一对差分信号线,时钟频率625MHz,在时钟信号的上升沿和下降沿均采样。

首先是硬件底板连接图。

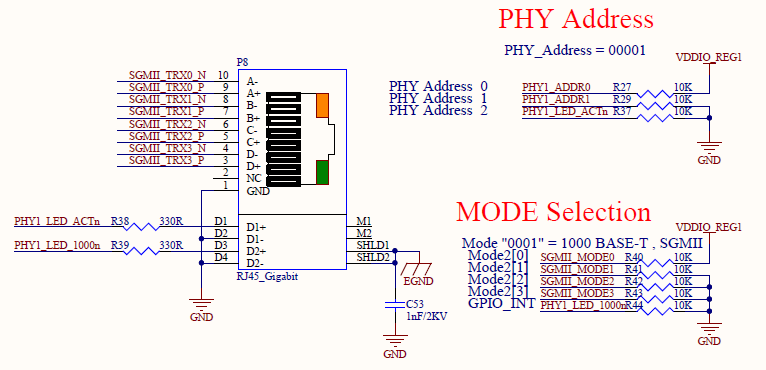

其次是网口座子和PHY芯片的模式选择引脚以及PHY地址的接线图:

查阅AR8031的数据手册,先看硬件定义如下:

可见此接口引脚数量为4个,收发各一对差分信号线。

参考时钟RX_CLK由PHY提供,是可选的,主要用于MAC侧没有时钟的情况,一般情况下,RX_CLK不使用,收发都可以从数据中恢复出时钟。

其实,大多数MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),直接外接光模块,而不需要PHY层芯片,此时时钟速率仍旧是625MHz,不过此时跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因为插入了控制信息,而SerDes端口速率被提高是因为进行了8B/10B变换,本来8B/10B变换是PHY芯片的工作,在SerDes接口中,因为外面不接PHY芯片,此时8B/10B变换在MAC芯片中完成了。8B/10B变换的主要作用是扰码,让信号中不出现过长的连“0”和连“1”情况,影响时钟信息的提取