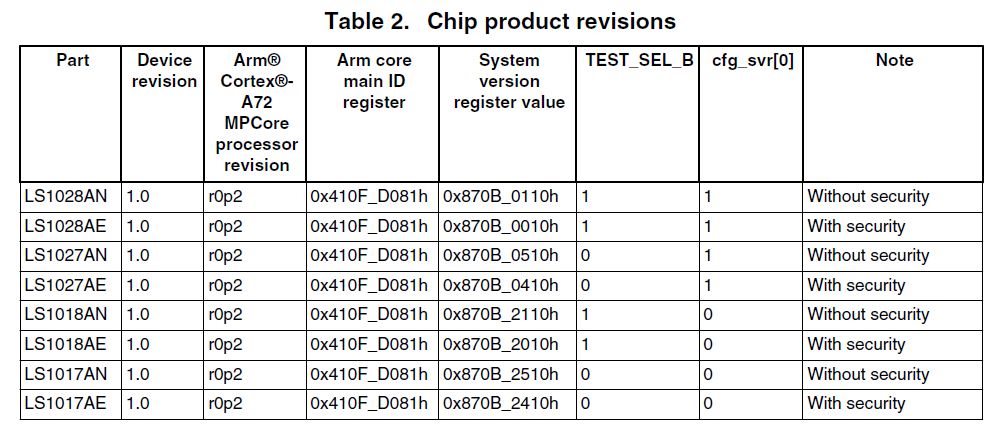

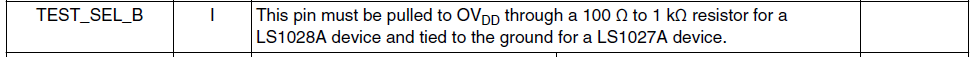

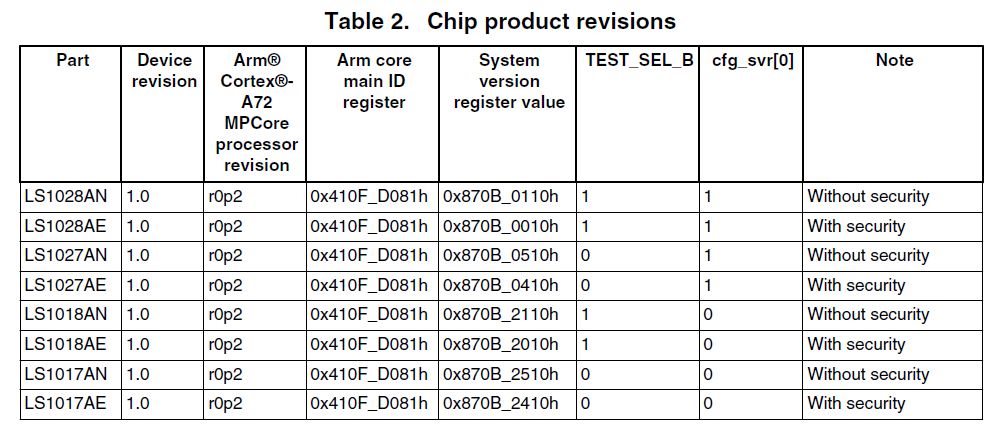

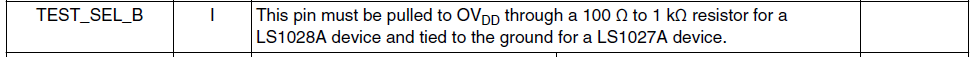

日前在解决问题的时候,因为要排除某些因素,所以想要减少Linux系统中使用的CPU的核心,之前在LS1028平台,可以通过TEST_SEL_B和cfg_svr[0]直接更改其变成其他的型号,参见以下内容:

比如可以通过将cfg_svr[0]置低以变成LS1018,以实现将双核变成单核的效果。

日前在解决问题的时候,因为要排除某些因素,所以想要减少Linux系统中使用的CPU的核心,之前在LS1028平台,可以通过TEST_SEL_B和cfg_svr[0]直接更改其变成其他的型号,参见以下内容:

比如可以通过将cfg_svr[0]置低以变成LS1018,以实现将双核变成单核的效果。

前段时间接到一个工作,是要在OK1028A-C的开发板上移植一下OpenWRT系统,在之前的OpenWRT版本是,原本是不支持LS1028的SOC的,不过在最新的版本上增加了支持。

其实LSxx系列的开发板,像是LS1012,1043,1046很早之前就支持了OpenWRT系统,不过的处理方式也简单很多,使用OpenWRT源码编译完成之后,只要它编译出来的内核设备树以及文件系统,像是U-boot以及引导方面的固件还是使用发布资料中的LSDK的镜像来实现。关于这部分的内容,博客中之前的博文也有很多提到了,可以参考了解一下:https://resona.top/tags/OpenWRT/

原本这次的工作也是按照这个方法来做的,这样的实现起来简单很多。但是资料交付给客户之后,客户说他必须需要OpenWRT系统中的使用网页界面升级的功能,这一下就难搞很多了呀。

这样就必须要按照OpenWRT的原生镜像的格式来制作,烧写到板子上的系统的结构也需要和OpenWRT的原生的结构保持一致才行。

目前在做RK3588的Ubuntu22.04的系统移植工作的时候,发现了Github上一个非常好的项目https://github.com/Joshua-Riek/ubuntu-rockchip

目前我也是在基于这个项目上的代码再做开发,今天的文章不再多说这些,主要是分享在移植过程中看到的两个比较好用的服务。

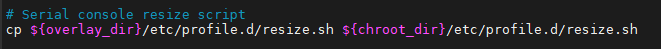

一个是开机之后自动调整串口的窗口大小的resize.sh

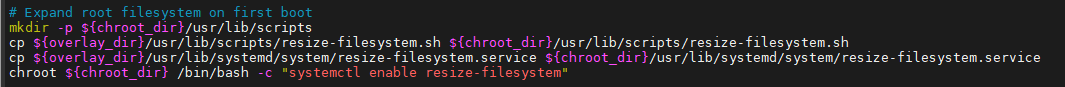

另一个是会在第一次启动时自动扩展文件系统分区的resize-filesystem.sh

如果有需要的话可以参照着这个放到自己的文件系统上去,但是需要注意的是自动扩展文件系统分区的这个脚本有坑。

今天腾讯云通知我域名的SSL证书到期了,所以我自己又在腾讯云上重新申请了一年的免费的SSL证书。

突然意识到自己已经建站两年多了,也一直是处于自娱自乐佛系更新的阶段。没有像其他的大神一样通过博客交到很多志同道合的朋友,也没有遵从一开始建站的心愿好好记录一下生活或者是工作中易忘的知识,最终还是要慢慢的腐朽成一个空壳子么?

… 其他的感慨有时间再慢慢絮叨吧 … 今天的目的还是要好好记录一下最近的博客的更新变化呢。

很久之前在微信关注了一个【逛逛Github】的订阅号,它会时不时推荐一些好玩的GitHub上的项目,最近我被一个Memos备忘录的项目吸引了,项目链接如下:https://github.com/usememos/memos

这个是干啥的还有搭建过程就不多说了,上面有很详细的介绍,就是可以实现一个类似QQ空间说说的功能,而且搭建直接使用docker也很简单,搭建好的端口默认运行在5230。

搭建好之后,除了在网页上可以直接访问之外,也有很多大神做了三方的客户端可以使用,比如iPhone上可以使用的Moe Memos,当然我就要下载下来试一下呀。可是在填写服务器地址的时候出了问题,Apple为了安全必须要https的地址,但是docker搭建的Memos的是http的呀,这可怎么办才好呢?

下文中是归纳了一些在linux控制台查看网口收发包统计的一些信息